SigmanticAI – Automatisierung der Hardwareverifikation

Dieses Tool bewerten

Durchschnittsbewertung

Gesamtstimmen

Wähle deine Bewertung (1-10):

Detailinformationen

Was

SigmanticAI ist ein KI-basiertes Automatisierungsprodukt für die Hardware-Verifikation, das sich an Halbleiter- und digitale Verifikationsteams richtet. Der Schwerpunkt liegt auf der Generierung von Verifikationsartefakten wie UVM-Testbenches, eingeschränkten Stimuli, funktionaler Coverage, Assertions und Registermodellen aus natürlichsprachigen Spezifikationen oder RTL-Kontext.

Das Produkt ist als Beschleuniger für bestehende Design-Verifikations-Workflows positioniert und nicht als Ersatz für Ingenieure oder Simulatoren. Sein zentraler Mehrwert besteht darin, den manuellen Aufwand für das Schreiben von boilerplateartigem Verifikationscode zu reduzieren und Teams dabei zu helfen, schneller eine aussagekräftige Coverage zu erreichen, während die Ausgaben mit etablierten DV-Flows kompatibel bleiben.

Funktionen

- Generierung von UVM-Testbenches: Erstellt UVM-Umgebungen, Agents, Sequenzen und Scoreboards aus Spezifikationen, sodass Teams den manuellen Einrichtungsaufwand reduzieren und früher mit der Simulation beginnen können.

- Erstellung coverage-gesteuerter Stimuli: Erzeugt gerichtete und constrained-random Stimuli, die an Coverage-Ziele gekoppelt sind, wodurch sich Verifikationsaktivitäten auf das konzentrieren können, was noch getestet werden muss.

- Generierung funktionaler Coverage-Modelle: Erstellt Coverage-Modelle, die den Verifikationsfortschritt strukturiert nachverfolgen und die Coverage-Closure unterstützen sollen.

- Generierung von Assertions: Erzeugt automatisch Protokoll-, Sicherheits- und Korrektheits-Assertions in SVA/PSL, um die Prüfung zu stärken und Probleme früher im Flow zu erkennen.

- Registerdefinitionen und -zuordnungen: Generiert simulationsbereite Registermodelle und Zuordnungen, was den wiederkehrenden Aufwand für die Erstellung von Registermodellen reduzieren kann.

- Geeignet für bestehende Umgebungen: Laut Website arbeitet das Produkt mit bestehenden Simulatoren und Flows, respektiert IP-Grenzen und kann On-Premises oder in kontrollierten Umgebungen bereitgestellt werden.

Hilfreiche Tipps

- Ausgaben anhand interner Standards validieren: Auch wenn generierte Artefakte als produktionsreif beschrieben werden, sollten Teams sie im Hinblick auf Namenskonventionen, methodische Eignung und projektspezifische Verifikationsabsichten prüfen.

- Mit klar abgegrenzten Anwendungsfällen beginnen: Die anfängliche Einführung ist oft einfacher, wenn das Tool zunächst auf einen einzelnen IP-Block, einen Interface-Agenten oder ein Assertions-Set angewendet wird, bevor es auf ein umfassenderes DV-Programm ausgeweitet wird.

- Wert anhand von Workflow-Ergebnissen messen: Bei Tools dieser Kategorie sollte sich die praktische Bewertung auf Prüfaufwand, Simulationsbereitschaft, Coverage-Fortschritt und die Reduzierung repetitiver Codierung konzentrieren.

- Eignung im Hinblick auf Sicherheit und IP-Handhabung prüfen: Wenn Verifikationsartefakte aus sensiblen Spezifikationen oder RTL erstellt werden, sollten Bereitstellungsmodell und Kontrollen für IP-Grenzen Teil der Bewertung sein.

- Anforderungen an die Qualität der Eingabequellen klären: Da die Generierung von natürlichsprachigen Spezifikationen oder RTL-Kontext abhängt, wird die Ausgabequalität wahrscheinlich davon beeinflusst, wie vollständig und strukturiert diese Eingaben sind.

OpenClaw-Fähigkeiten

Innerhalb des OpenClaw-Ökosystems könnte SigmanticAI voraussichtlich Fähigkeiten für Verifikationsplanung, Orchestrierung der Artefaktgenerierung und Review-Workflows unterstützen. Ein plausibler OpenClaw-Agent könnte Designspezifikationen einlesen, Verifikationsziele identifizieren, Prompts oder Kontext an SigmanticAI weiterleiten und anschließend die resultierenden UVM-Komponenten, Assertions und Coverage-Artefakte in projektspezifischen Workstreams organisieren. Die Seite beschreibt keine native OpenClaw-Integration, daher sollte dies eher als wahrscheinliches Workflow-Muster denn als bestätigte Funktion behandelt werden.

Diese Kombination könnte besonders nützlich für Design-Verifikationsleiter, CAD-Teams und Projektmanager sein, die eine engere Abstimmung zwischen Anforderungen, generierten Artefakten und Sign-off-Fortschritt benötigen. Wahrscheinliche OpenClaw-Workflows könnten Agenten für die Rückverfolgbarkeit von Spezifikation zu Verifikation, Assistenten zur Vorbereitung von Regressionen, Agenten zur Bewertung von Coverage-Lücken und Review-Copiloten umfassen, die generierte Artefakte mit internen Standards vergleichen. In der Praxis könnte dies Verifikationsteams stärker auf Aufgaben mit höherem Hebel ausrichten, etwa auf Edge-Case-Strategien, Validierung auf Architekturebene und teamübergreifende Koordination, während der Zeitaufwand für repetitive Gerüsterstellung reduziert wird.

Einbettungscode

Teile dieses KI-Tool auf deiner Website oder in deinem Blog, indem du den folgenden Code kopierst und einfügst. Das eingebettete Widget aktualisiert sich automatisch.

<iframe src="https://www.aimyflow.com/ai/sigmanticai-com/embed" width="100%" height="400" frameborder="0"></iframe>

Ähnliche Tools entdecken

Noetic | Erreichen Sie Hardware-Compliance in Wochen, nicht in Monaten

Noetic ist eine KI-gestützte Plattform für Hardware-Compliance, die Hardware-Teams dabei unterstützt, relevante Vorschriften zu identifizieren, technische Dokumentation zu erstellen und schneller geeignete Prüflabore zu finden. Für Compliance-, Regulatory- und Engineering-Funktionen kann sie den Weg von der Normenrecherche bis zur laborreifen Dokumentation verkürzen, indem sie Anforderungen, Dokumente und Statusaktualisierungen an einem Ort zusammenführt.

Semble AI – KI-gestützte Planung von Gebäudesystemen

Semble AI ist eine KI-gestützte Plattform für die Planung von Gebäudesystemen, die Ingenieur- und Bauteams dabei unterstützt, Grundrisse hochzuladen, Geräte zu platzieren, die Einhaltung von Bauvorschriften zu prüfen und Layouts sowie Stücklisten zu erstellen; der derzeitige Live-Support konzentriert sich auf Brandschutzsysteme. Für Planer im Brandschutz, MEP-Ingenieure und Planprüfer kann sie die wiederkehrende Recherche zu Vorschriften und die Planungsarbeit verkürzen, indem KI-generierte Layouts mit zitierten Vorschriftenanforderungen und Projektdokumenten verknüpft werden.

Normale Fabrik

Normal Factory ist eine Plattform für Hardwaretests und Zertifizierungen, die Unternehmen dabei unterstützt, die Konformität mit Standards wie FCC, ISED, CE und ASTM vorzubereiten und zu verwalten – durch Pre-Compliance-Software und einen schrittweisen Prozess, vor allem für Hardware-Teams, die Produkte auf den Markt bringen. Für Fachkräfte in den Bereichen Hardware, Compliance und Betrieb kann sie den manuellen Koordinationsaufwand reduzieren und die Zertifizierungsarbeit bei der Prüfung, Dokumentation und dem Weg zur Marktzulassung beschleunigen.

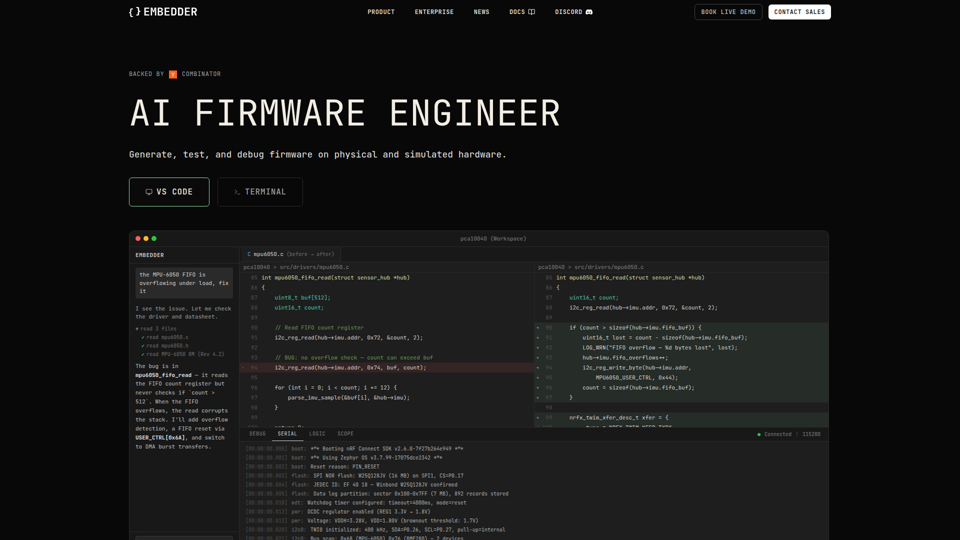

Embedder | KI-Firmware-Ingenieur

Embedder ist ein KI-Tool für Firmware-Engineering, das verifizierte C++- und Rust-Firmware aus Datenblättern und Hardwaredokumenten für Embedded- und Firmware-Ingenieure erstellt, testet und debuggt, die mit MCUs und Peripheriegeräten arbeiten. Durch die Verankerung des Codes in der Quelldokumentation und seine Validierung auf simulierter und physischer Hardware kann es Embedded-Teams dabei helfen, Fehler bei der Interpretation von Datenblättern zu reduzieren und die Treiberentwicklung sowie das Debugging zu beschleunigen.

Stillwind

Stillwind ist ein KI-Suchwerkzeug für die Elektrotechnik, das Nutzern hilft, mit natürlichsprachlichen Abfragen elektronische Bauteile zu finden, indem detaillierte Spezifikationen mit einer großen Bauteildatenbank abgeglichen werden. Es richtet sich vor allem an Elektroingenieure und Embedded-Softwareentwickler. In KI-gestützten Hardware-Workflows kann es den Zeitaufwand für die Komponentenrecherche verringern und verbessern, wie Ingenieure und sourcingbezogene Teams Designanforderungen in präzise Bauteilauswahlen umsetzen.

Zettaskala

Zettascale ist ein Hardwareunternehmen aus dem Silicon Valley, das energieeffiziente, rekonfigurierbare XPU-Chips für KI-Training und -Inferenz entwickelt, vor allem für Teams, die fortschrittliche KI-Recheninfrastruktur aufbauen. Für KI-Hardware-, Compiler- und Systemingenieure können modelloptimierter Datenfluss und reduzierte Speicherbewegung den Durchsatz verbessern und gleichzeitig den Energieverbrauch bei Trainings- und Inferenz-Workloads senken.

Deepnight - Nachtsicht der nächsten Generation

Deepnight ist ein KI-Nachtsichtsystem, das Schwachlichtsensoren mit Bildverarbeitung kombiniert, um sehr dunkle Szenen in lebendige Farben und ein breiteres Sichtfeld zu verwandeln, vor allem für Organisationen, die in den Bereichen nächtliche Navigation, Überwachung und Sicherheit tätig sind. Für Teams im Bereich autonomer Fahrzeuge, Forschende, landwirtschaftliche Betriebe und Verteidigungsaufgaben kann es die Entscheidungsfindung bei schlechten Lichtverhältnissen verbessern, indem es eine stabilere Echtzeit-Sicht über wechselnde Umgebungen hinweg bietet.

Silogy

Silogy entwickelt Viv, einen On-Premise-KI-Verifikationsingenieur, der Protokolle, Code, Wellenformen und Testergebnisse analysiert, um fehlschlagende Regressionen im Digitaldesign schneller zu debuggen – hauptsächlich für Chipentwickler und Verifikationsingenieure. Für Halbleiter-Verifikationsteams kann dies die repetitive Root-Cause-Analyse automatisieren und übergabereife Debug-Erkenntnisse beschleunigen, während sensible Designdaten auf internen Servern bleiben.