SigmanticAI - Automatización de la verificación de hardware

Valora esta herramienta

Puntuación media

Votos totales

Selecciona tu puntuación (1-10):

Información detallada

Qué

SigmanticAI es un producto de automatización de verificación de hardware basado en IA para equipos de semiconductores y verificación digital. Se centra en generar artefactos de verificación como testbenches UVM, estímulos restringidos, cobertura funcional, aserciones y modelos de registros a partir de especificaciones en lenguaje natural o del contexto RTL.

El producto está posicionado como un acelerador de flujo de trabajo para entornos de verificación de diseño existentes, en lugar de un reemplazo para ingenieros o simuladores. Su valor principal es reducir el esfuerzo manual que implica escribir código repetitivo de verificación y ayudar a los equipos a alcanzar una cobertura significativa más rápido, manteniendo al mismo tiempo la compatibilidad de los resultados con los flujos de DV establecidos.

Funcionalidades

- Generación de testbench UVM: Crea entornos UVM, agentes, secuencias y scoreboards a partir de especificaciones para que los equipos puedan reducir el trabajo manual de configuración y comenzar la simulación antes.

- Creación de estímulos impulsada por cobertura: Produce estímulos dirigidos y aleatorios restringidos vinculados a objetivos de cobertura, lo que ayuda a centrar los esfuerzos de verificación en lo que aún debe ejercitarse.

- Generación de modelos de cobertura funcional: Construye modelos de cobertura diseñados para realizar un seguimiento estructurado del progreso de verificación y respaldar el trabajo de cierre de cobertura.

- Generación de aserciones: Genera automáticamente aserciones de protocolo, seguridad y corrección en SVA/PSL para reforzar las comprobaciones y detectar problemas antes en el flujo.

- Definiciones y mapeos de registros: Genera modelos y mapeos de registros listos para simulación, lo que puede reducir el esfuerzo repetitivo de creación de modelos de registros.

- Implementación adecuada para entornos existentes: El sitio indica que el producto funciona con simuladores y flujos existentes, respeta los límites de la propiedad intelectual y puede implementarse on-prem o en entornos controlados.

Consejos útiles

- Validar la salida según los estándares internos: Incluso cuando los artefactos generados se describen como listos para producción, los equipos deben revisarlos en cuanto a convenciones de nomenclatura, adecuación metodológica e intención de verificación específica del proyecto.

- Comenzar con casos de uso acotados: La adopción inicial suele ser más sencilla cuando se aplica a un único bloque IP, agente de interfaz o conjunto de aserciones antes de ampliarse a un programa de DV más amplio.

- Medir el valor a través de resultados del flujo de trabajo: En herramientas de esta categoría, la evaluación práctica debe centrarse en el esfuerzo de revisión, la preparación para simulación, el progreso de cobertura y la reducción de la codificación repetitiva.

- Comprobar la adecuación con necesidades de seguridad y manejo de IP: Si los activos de verificación se construyen a partir de especificaciones sensibles o RTL, el modelo de implementación y los controles de límites de IP deben formar parte de la evaluación.

- Aclarar los requisitos de calidad de las entradas de origen: Dado que la generación depende de especificaciones en lenguaje natural o del contexto RTL, es probable que la calidad de la salida dependa de cuán completas y estructuradas estén esas entradas.

Habilidades de OpenClaw

Dentro del ecosistema OpenClaw, SigmanticAI probablemente podría dar soporte a habilidades para planificación de verificación, orquestación de generación de artefactos y flujos de revisión. Un agente plausible de OpenClaw podría ingerir especificaciones de diseño, identificar objetivos de verificación, dirigir prompts o contexto a SigmanticAI y luego organizar los componentes UVM, las aserciones y los activos de cobertura resultantes en flujos de trabajo específicos del proyecto. La página no describe una integración nativa con OpenClaw, por lo que esto debe considerarse un patrón de flujo de trabajo probable y no una capacidad confirmada.

Esta combinación podría ser especialmente útil para responsables de verificación de diseño, equipos CAD y gestores de proyectos que necesiten una coordinación más estrecha entre requisitos, activos generados y progreso hacia el signoff. Los flujos de trabajo probables de OpenClaw podrían incluir agentes de trazabilidad de especificación a verificación, asistentes de preparación de regresión, agentes de triaje de brechas de cobertura y copilotos de revisión que comparen los artefactos generados con los estándares internos. En la práctica, eso podría desplazar a los equipos de verificación hacia tareas de mayor valor, como la estrategia de casos límite, la validación a nivel de arquitectura y la coordinación entre equipos, al tiempo que reduce el tiempo dedicado a tareas repetitivas de andamiaje.

Código de inserción

Comparte esta herramienta de IA en tu sitio o blog copiando y pegando el código. El widget insertado se actualizará automáticamente con la información más reciente.

<iframe src="https://www.aimyflow.com/ai/sigmanticai-com/embed" width="100%" height="400" frameborder="0"></iframe>

Explorar herramientas similares

Noetic | Logre el cumplimiento de hardware en semanas, no en meses

Noetic es una plataforma de cumplimiento normativo de hardware impulsada por IA que ayuda a los equipos de hardware a identificar las regulaciones aplicables, redactar documentación técnica y encontrar laboratorios de ensayo adecuados más rápido. Para las funciones de cumplimiento, regulación e ingeniería, puede acortar el camino desde la investigación de normas hasta la documentación lista para laboratorio al mantener los requisitos, los documentos y las actualizaciones de estado en un solo lugar.

Semble AI - Diseño de sistemas de edificios impulsado por IA

Semble AI es una plataforma de diseño de sistemas de edificios impulsada por IA que ayuda a los equipos de ingeniería y construcción a cargar planos, colocar dispositivos, verificar el cumplimiento de los códigos de construcción y generar diseños y listas de materiales, con soporte activo actual centrado en los sistemas contra incendios. Para diseñadores de protección contra incendios, ingenieros MEP y revisores de planos, puede reducir el trabajo repetitivo de investigación normativa y elaboración de planos al vincular los diseños generados por IA con los requisitos normativos citados y los documentos del proyecto.

Fábrica normal

Normal Factory es una plataforma de pruebas y certificación de hardware que ayuda a las empresas a prepararse para cumplir y gestionar la conformidad con normas como FCC, ISED, CE y ASTM mediante software de preconformidad y un proceso paso a paso, principalmente para equipos de hardware que llevan productos al mercado. Para profesionales de hardware, cumplimiento y operaciones, puede reducir la coordinación manual y hacer que el trabajo de certificación sea más rápido de revisar, documentar y avanzar hacia la aprobación para su comercialización.

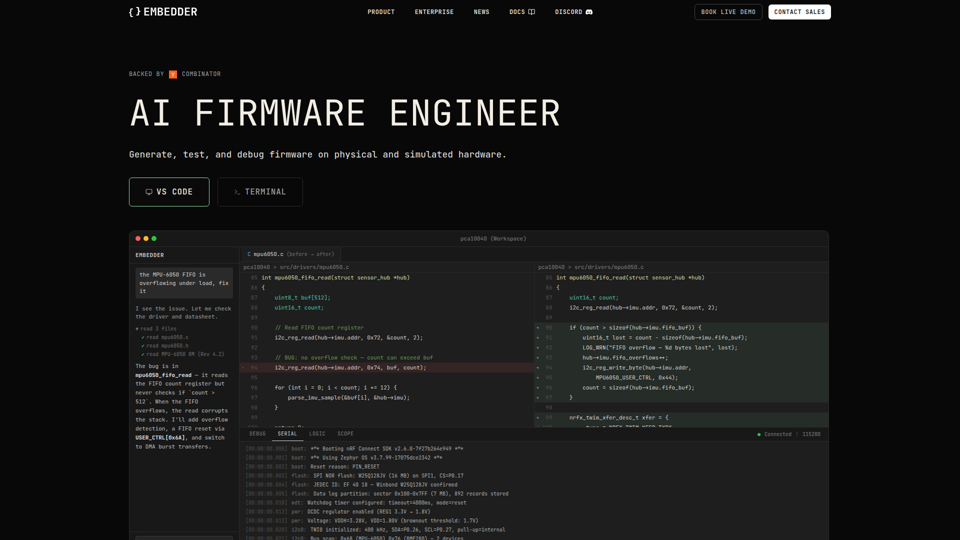

Ingeniero de firmware de IA | Integración de modelos embebidos

Embedder es una herramienta de ingeniería de firmware con IA que genera, prueba y depura firmware verificado en C++ y Rust a partir de hojas de datos y documentación de hardware para ingenieros de sistemas embebidos y firmware que trabajan con MCU y periféricos. Al basar el código en la documentación fuente y validarlo en hardware simulado y físico, puede ayudar a los equipos de sistemas embebidos a reducir los errores de interpretación de hojas de datos y acelerar el desarrollo y la depuración de controladores.

Todavíaviento

Stillwind es una herramienta de búsqueda con IA para ingeniería eléctrica que ayuda a los usuarios a encontrar componentes electrónicos mediante consultas en lenguaje natural, al comparar especificaciones detalladas con una amplia base de datos de piezas, principalmente para ingenieros eléctricos y desarrolladores de software embebido. En los flujos de trabajo de hardware asistidos por IA, puede reducir el tiempo de investigación de componentes y mejorar la forma en que los ingenieros y los equipos relacionados con abastecimiento traducen las necesidades de diseño en selecciones precisas de componentes.

Zettascala

Zettascale es una empresa de hardware de Silicon Valley que desarrolla chips XPU reconfigurables y energéticamente eficientes para el entrenamiento y la inferencia de IA, principalmente para equipos que desarrollan infraestructura avanzada de cómputo para IA. Para ingenieros de hardware, compiladores y sistemas de IA, el flujo de datos optimizado para modelos y la reducción del movimiento de memoria pueden mejorar el rendimiento mientras disminuyen el consumo energético en cargas de trabajo de entrenamiento e inferencia.

Deepnight - Visión Nocturna de Próxima Generación

Deepnight es un sistema de visión nocturna con IA que combina sensores de baja luminosidad con procesamiento de imágenes para convertir escenas muy oscuras en color vívido y un campo de visión más amplio, principalmente para organizaciones que trabajan en navegación nocturna, monitoreo y seguridad. Para equipos de vehículos autónomos, investigadores, operadores agrícolas y funciones de defensa, puede mejorar la toma de decisiones en condiciones de poca luz al proporcionar una visibilidad más estable y en tiempo real en entornos cambiantes.

Silogía

Silogy desarrolla Viv, un ingeniero de verificación de IA local que analiza registros, código, formas de onda y salidas de pruebas para depurar más rápido las regresiones fallidas de diseño digital, principalmente para desarrolladores de chips e ingenieros de verificación. Para los equipos de verificación de semiconductores, esto puede automatizar el análisis repetitivo de causa raíz y acelerar la generación de hallazgos de depuración listos para transferencia, manteniendo los datos de diseño sensibles en servidores internos.