SigmanticAI - Hardware Verification Automation

Rate this Tool

Average Score

Total Votes

Select your score (1-10):

Detail Information

What

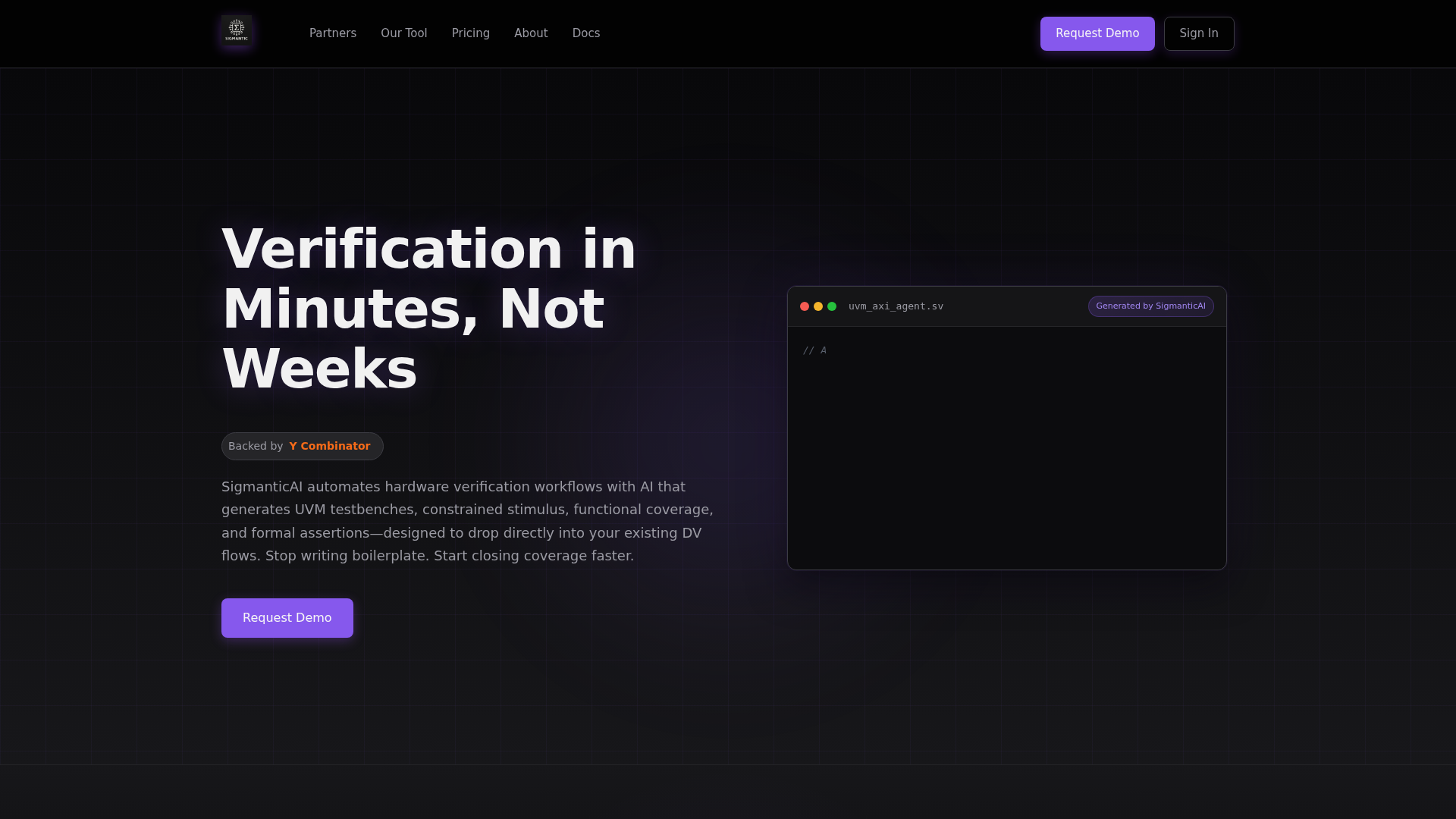

SigmanticAI is an AI-based hardware verification automation product for semiconductor and digital verification teams. It focuses on generating verification artifacts such as UVM testbenches, constrained stimulus, functional coverage, assertions, and register models from natural-language specifications or RTL context.

The product is positioned as a workflow accelerator for existing design verification environments rather than a replacement for engineers or simulators. Its core value is reducing the manual effort involved in writing boilerplate verification code and helping teams reach meaningful coverage faster while keeping outputs compatible with established DV flows.

Features

- UVM testbench generation: Creates UVM environments, agents, sequences, and scoreboards from specifications so teams can reduce manual setup work and start simulation sooner.

- Coverage-driven stimulus creation: Produces directed and constrained-random stimulus tied to coverage goals, which helps verification efforts focus on what still needs to be exercised.

- Functional coverage model generation: Builds coverage models intended to track verification progress in a structured way and support coverage closure work.

- Assertion generation: Automatically generates protocol, safety, and correctness assertions in SVA/PSL to strengthen checking and catch issues earlier in the flow.

- Register definitions and mappings: Generates simulation-ready register models and mappings, which can reduce repetitive register-model authoring effort.

- Deployment fit for existing environments: The site states the product works with existing simulators and flows, respects IP boundaries, and can be deployed on-prem or in controlled environments.

Helpful Tips

- Validate output against internal standards: Even when generated artifacts are described as production-ready, teams should review them for naming conventions, methodology fit, and project-specific verification intent.

- Start with bounded use cases: Initial adoption is often easier when applied to a single IP block, interface agent, or assertion set before expanding across a broader DV program.

- Measure value through workflow outcomes: For tools in this category, practical evaluation should focus on review effort, simulation readiness, coverage progress, and reduction in repetitive coding.

- Check fit with security and IP handling needs: If verification assets are built from sensitive specs or RTL, deployment model and IP-boundary controls should be part of the evaluation.

- Clarify source-input quality requirements: Since generation depends on natural-language specs or RTL context, output quality will likely depend on how complete and structured those inputs are.

OpenClaw Skills

Within the OpenClaw ecosystem, SigmanticAI could likely support skills for verification planning, artifact generation orchestration, and review workflows. A plausible OpenClaw agent could ingest design specs, identify verification targets, route prompts or context into SigmanticAI, then organize the resulting UVM components, assertions, and coverage assets into project-specific workstreams. The page does not describe a native OpenClaw integration, so this should be treated as a likely workflow pattern rather than a confirmed capability.

This combination could be especially useful for design verification leads, CAD teams, and project managers who need tighter coordination between requirements, generated assets, and signoff progress. Likely OpenClaw workflows might include spec-to-verification traceability agents, regression-prep assistants, coverage-gap triage agents, and review copilots that compare generated artifacts against internal standards. In practice, that could shift verification teams toward higher-leverage tasks such as edge-case strategy, architecture-level validation, and cross-team coordination, while reducing time spent on repetitive scaffolding.

Embed Code

Share this AI tool on your website or blog by copying and pasting the code below. The embedded widget will automatically update with the latest information.

<iframe src="https://www.aimyflow.com/ai/sigmanticai-com/embed" width="100%" height="400" frameborder="0"></iframe>

Explore Similar Tools

Noetic | Get Hardware Compliance Done in Weeks, Not Months

Noetic is an AI-powered hardware compliance platform that helps hardware teams identify applicable regulations, draft technical documentation, and find suitable testing labs faster. For compliance, regulatory, and engineering functions, it can shorten the path from standards research to lab-ready documentation by keeping requirements, documents, and status updates in one place.

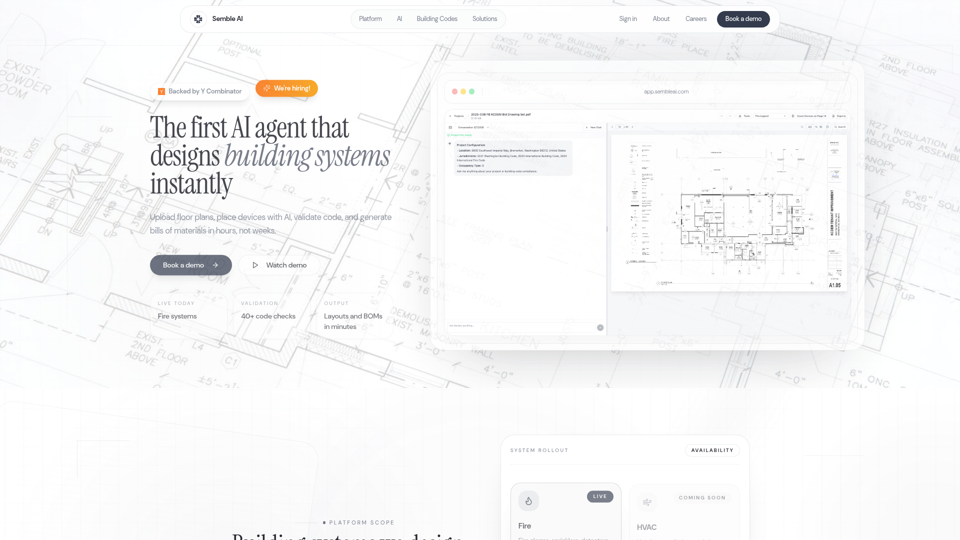

Semble AI - AI-Powered Building System Design

Semble AI is an AI-powered building system design platform that helps engineering and construction teams upload floor plans, place devices, check building-code compliance, and generate layouts and bills of materials, with current live support focused on fire systems. For fire protection designers, MEP engineers, and plan reviewers, it can shorten repetitive code research and drafting work by tying AI-generated layouts to cited code requirements and project documents.

Normal Factory

Normal Factory is a hardware testing and certification platform that helps companies prepare for and manage compliance for standards such as FCC, ISED, CE, and ASTM through pre-compliance software and a step-by-step process, mainly for hardware teams bringing products to market. For hardware, compliance, and operations professionals, it can reduce manual coordination and make certification work faster to review, document, and move toward market approval.

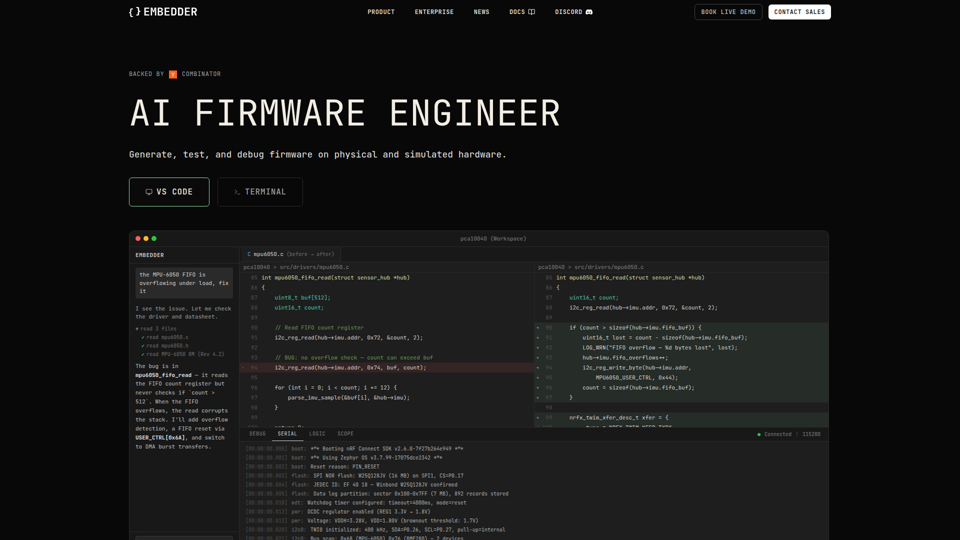

Embedder | AI Firmware Engineer

Embedder is an AI firmware engineering tool that generates, tests, and debugs verified C++ and Rust firmware from datasheets and hardware documents for embedded and firmware engineers working with MCUs and peripherals. By grounding code in source documentation and validating it on simulated and physical hardware, it can help embedded teams reduce datasheet interpretation errors and speed driver development and debugging.

Stillwind

Stillwind is an AI search tool for electrical engineering that helps users find electronic parts with natural language queries by matching detailed specifications against a large parts database, mainly for electrical engineers and embedded software developers. In AI-assisted hardware workflows, it can reduce component research time and improve how engineers and sourcing-related teams translate design needs into precise part selections.

Zettascale

Zettascale is a Silicon Valley hardware company building energy-efficient, reconfigurable XPU chips for AI training and inference, mainly for teams developing advanced AI compute infrastructure. For AI hardware, compiler, and systems engineers, model-optimized dataflow and reduced memory movement can improve throughput while lowering energy use in training and inference workloads.

Deepnight - Nextgen Night Vision

Deepnight is an AI night-vision system that combines low-light sensors with image processing to turn very dark scenes into vivid color and a wider field of view, mainly for organizations working in nighttime navigation, monitoring, and safety. For autonomous vehicle teams, researchers, agricultural operators, and defense functions, it can improve low-light decision-making by providing steadier, real-time visibility across changing environments.

Silogy

Silogy builds Viv, an on-premise AI verification engineer that analyzes logs, code, waveforms, and test outputs to debug failing digital design regressions faster, mainly for chip developers and verification engineers. For semiconductor verification teams, this can automate repetitive root-cause analysis and speed handoff-ready debug insights while keeping sensitive design data on internal servers.